1、功能设计阶段:设计目标产品的应用场合,设定一些诸如功能、性能、接口规格、温度、功耗等指标,作为后续电路设计的输入依据。根据市场和公司需求,完成芯片总体结构、规格参数、模块划分、使用技术以及各个功能模块的详细定义。总体设计规划完成后,再制定各个维度的设计方案。芯片设计方案按照自顶向下方式,逐级分解设计模块,形成各个模块的设计方案。

2、设计描述和行为级验证:依据芯片总体设计需求,可将SoC划分成若干功能模块,并决定这些功能模块是否需要使用IP核。该过程直接影响SoC的内部架构及各模块的顶层信号互连,并在后续设计过程中起到决定性作用,因此需要非常仔细谨慎地选择产品和IP核。 对于不需要使用IP核的模块,可使用VHDL/Verilog等硬件描述语言完成硬件电路各模块的设计工作。同时定义各个模块的功能点,按照功能点进行功能仿真验证和行为级验证。行为级仿真验证不考虑时序延时,因此无法覆盖时序相关问题,只能保证设计的功能正确性。时序延时的正确性需要通过其他手段实现。

3、逻辑综合:确定设计描述后,可使用逻辑综合工具对代码进行综合。综合过程需要选择适当的逻辑器件库和SDC时序约束文件,作为合成逻辑电路的综合参数。设计人员需要确定SDC约束文件的正确性,如果是IP核,IP核厂商会提供原版SDC约束文件,但并不适合芯片全局的SDC约束。因此,无论是使用的IP核,还是编写的verilog代码,均需要整理编写SDC约束文件。同时,SDC约束文件也是CDC/RDC代码规则检查的输入文件之一。

4、布局布线和后仿真:布局是指将设计好的功能模块合理地安排在芯片上,规划好它们的位置。布线是指完成各个模块之间的互连连线。 后仿真是仿真带有SDF延时参数的仿真,后仿真用于测试芯片的时序是否满足要求,功能性仿真在前仿时已经验证通过,因此后仿真更关注于仿真过程中的setup、hold time情况。对于后仿真出现的问题,需要定位问题点,判断是否需要后端修复、ECO修复或RTL重综合。

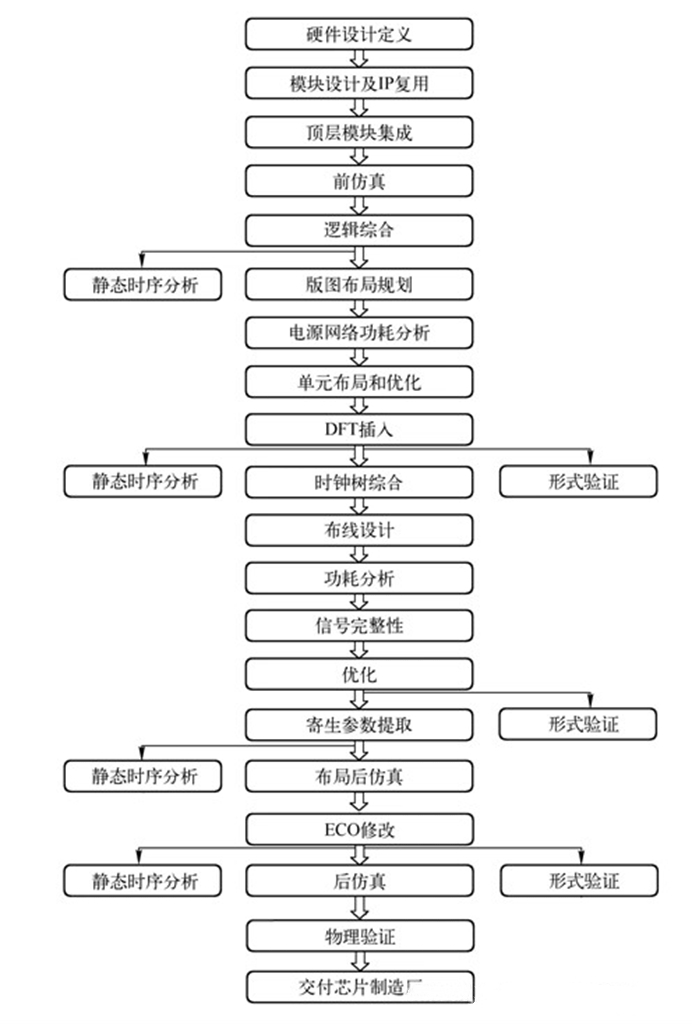

SOC的设计流程,包括数字电路设计前端和后端的全流程。具体各个部分又包括:

——硬件设计定义说明(Hardware Design Specification)

——模块设计及IP复用(Module Design & IP Reuse)

——顶层模块集成(Top Level Integration)

——前仿真(Pre-layout Simulation)

——逻辑综合(Logic Synthesis)

——版图布局规划(Floorplan)

——功耗分析(Power Analysis)

——单元布局和优化(Placement & Optimization)

——静态时序分析(STA,Static Timing Analysis)

——形式验证(Formal Verification)

——可测性电路插入(DFT,Design for Test)

——时钟树综合(Clock Tree Synthesis)

——布线设计(Routing)

——寄生参数提取(Parasitic Extraction)

——后仿真(Post-layout Simulation)

——ECO修改(ECO,Engineering Change Order)

——物理验证(Physical Verification)