常用的可测性设计方法包括基于扫描链(scan chain)的测试方法和内建自测试电路。

扫描链(SC)设计

时序电路的直接测试往往是难以实现的,扫描设计通常能很好的解决之一问题。

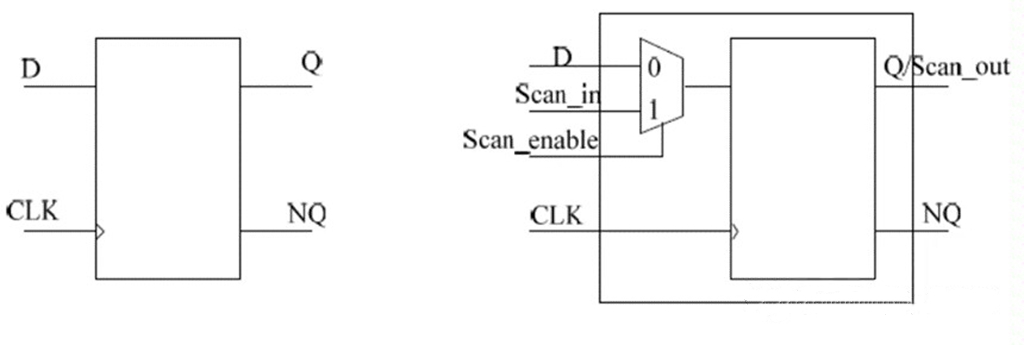

扫描设计的主要思想就是把难以进行测试的电路转化为可测的电路。要实现这一目标,需要把电路中原有的一般触发器用可观测可控制的扫描触发器进行代替,这些扫描触发器串接到一起形成扫描链(Scan Chain,SC),那么,在测试模式下,就可以通过扫描链来串行移入移出测试数据,实现对整个电路的控制和观测。单个扫描触发器代替一般触发器的例子如图:

从上图可以看到,扫描触发器在原始触发器的基础上在数据输入端D 增加了一个多路选择器,用以实现对输入数据的选择,其中Scan in 是扫描数据输入端口,Scan enable 是输入选择控制端,Scan out 复用原始输出端Q。常见的扫描触发器的工作模式有正常工作模式和扫描移位模式两种:

(1) 正常工作模式:Scan enable 为0 时,此时为正常工作模式,D 输入端选通,Q 作为输出端,数据从D 输入,从Q 输出;

(2) 扫描移位模式:Scan enable 为1 时,此时为扫描移位模式,Scan in输入端选通,Scan out 作为扫描输出,测试数据由Scan in 输入,由Scan out 输出。

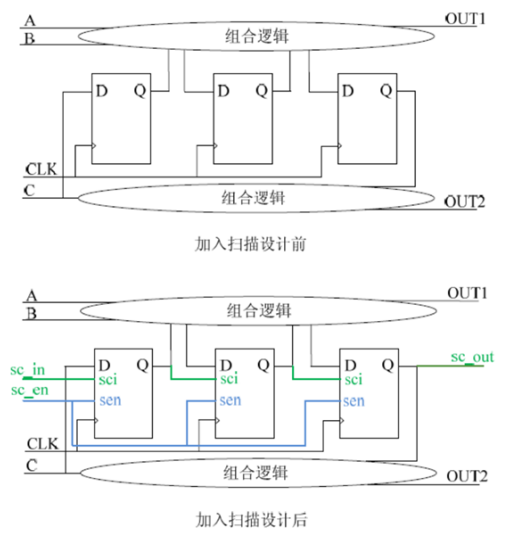

将扫描触发器单元连接在一起,就构成了扫描设计的基本结构。根据是否所有的寄存器都是扫描单元并已连接到扫描链,可以将扫描设计分为全扫描和部分扫描。通常为了提高电路的性能,我们往往排除那些不符合可测性设计规则的寄存器,这样设计得到的电路一般介于全扫描和部分扫描之间。

对加入扫描设计后的电路进行测试时,我们首先设置模式选择端sc_en 为1,电路处于扫描移位模式,向扫描输入端口sc_in 打入测试向量,比如101,通过扫描链传至每个扫描寄存器;然后我们设置sc_en 端口为0,电路进入正常工作模式,并行向三个原始输入端口A,B,C 打入激励;从输出端口Q 捕获响应数据,分析响应数据就可以达到测试目的。