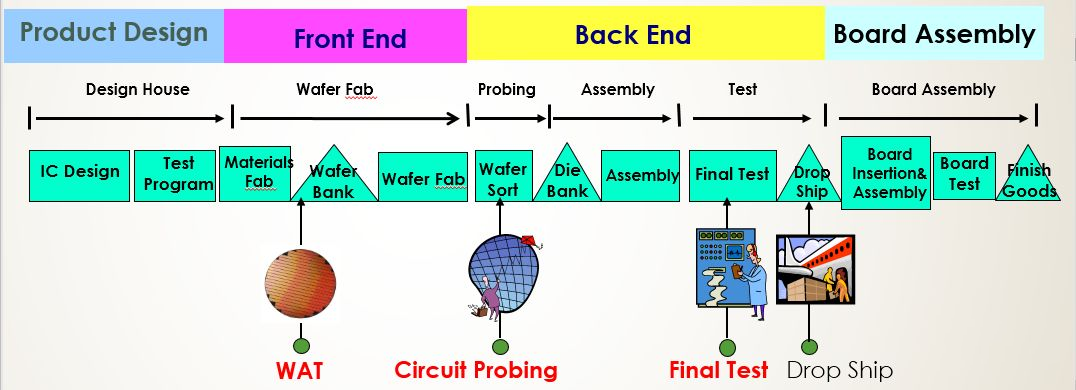

半导体生产流程由晶圆制造,晶圆测试,芯片封装和封装后测试组成,而测试环节主要集中在WAT,CP和FT三个环节。

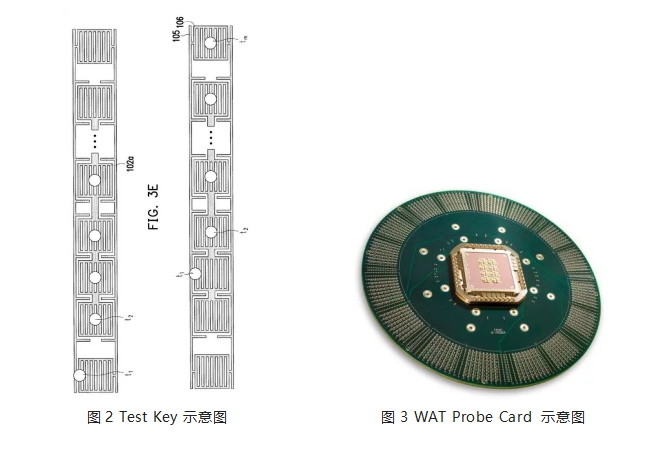

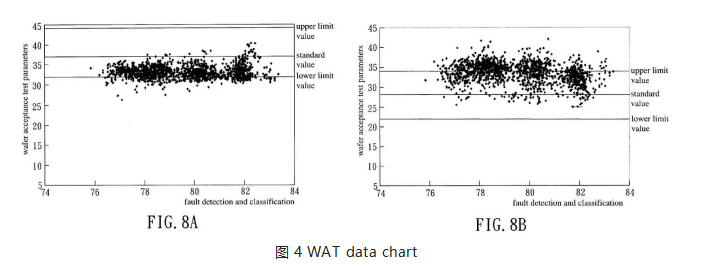

WAT(Wafer Acceptance Test)测试,也叫PCM(Process Control Monitoring),对Wafer 划片槽(Scribe Line)测试键(Test Key)的测试,通过电性参数来监控各步工艺是否正常和稳定,例如CMOS的电容,电阻, Contact,Metal Line 等,一般在wafer完成制程前,是Wafer从Fab厂出货到封测厂的依据,测试方法是用Probe Card扎在Test Key的Metal Pad上,Probe Card另一端接在WAT测试机台上,由WAT Recipe自动控制测试位置和内容,测完某条Test Key后,Probe Card会自动移到下一条Test Key,直到整片Wafer测试完成。WAT测试有问题,超过SPEC,一般对应Fab各个Module制程工艺或者机台Shift,例如Litho OVL异常,ETCH CD 偏小,PVD TK偏大等等。WAT有严重问题的Wafer会直接报废。

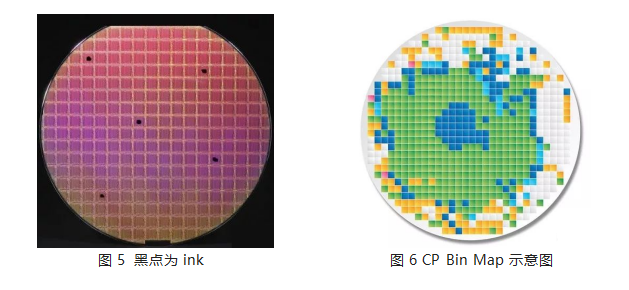

CP(Circuit Probing)也叫“Wafer Probe”或者“Die Sort”,是对整片Wafer的每个Die的基本器件参数进行测试,例如Vt(阈值电压),Rdson(导通电阻),BVdss(源漏击穿电压),Igss(栅源漏电流),Idss(漏源漏电流)等,把坏的Die挑出来,会用墨点(Ink)标记,可以减少封装和测试的成本,CP pass才会封装,一般测试机台的电压和功率不高,CP是对Wafer的Die进行测试,检查Fab厂制造的工艺水平。

CP测试程序和测试方法优化是Test Engineer努力的方向,下面介绍几种降低CP测试成本的方法。

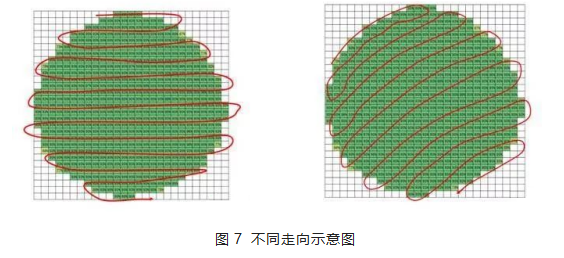

1.同一个Probe Card可以同时测多个Die,如何排列可以减少测试时间?假设Probe Card可以同时测6个Die,那么是2×3排列还是3×2,或者1×6,都会对扎针次数产生影响,不同的走针方向,也会产生Test时间问题。

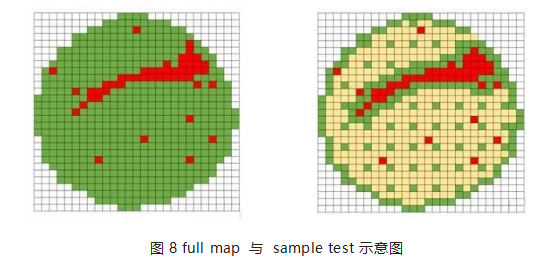

2.随着晶圆尺寸越来越大,晶圆上的Die越来越多,很多公司CP Test会采用抽样检查(Sampling Test)的方式来减少测试时间,至于如何抽样,涉及不同的Test Recipe,一些大数据实时监控软件可以在测试的同时按照一定算法控制走针方向,例如抽测到一个Die失效后,Probe Card会自动围绕这个Die周围一圈测试,直到测试没有问题,再进行下一个Die的抽测,这种方法可以明显缩短测试时间。

FT(final test)是对封装好的Chip进行Device应用方面的测试,把坏的chip挑出来,FT pass后还会进行process qual和product qual,FT是对package进行测试,检查封装造厂的工艺水平。FT的良率一般都不错,但由于FT测试比CP包含更多的项目,也会遇到Low Yield问题,而且这种情况比较复杂,一般很难找到root cause。广义上的FT也称为ATE(Automatic Test Equipment),一般情况下,ATE通过后可以出货给客户,但对于要求比较高的公司或产品,FT测试通过之后,还有SLT(System Level Test)测试,也称为Bench Test。SLT测试比ATE测试更严格,一般是功能测试,测试具体模块的功能是否正常。

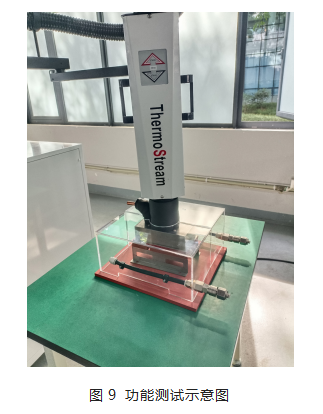

成都中冷低温的ThermoTST TS-780高低温冲击气流仪以速度、精度和可靠性作为基本设计标准,提供了非常先进的温度测试能力。温度转换从-55℃到+125℃之间转换约10秒,并有更广泛的温度范围-80℃到+225℃; 经长期的多工况验证,满足更多生产环境和工程环境的要求。 TS-780应用于提供老化测试、特性分析、高低温温变测试、温度冲击测试、失效分析等可靠性试验,用于芯片、微电子器件、集成电路 (SOC、FPGA、PLD、MCU、ADC/DAC、DSP 等) 、闪存 Flash、UFS、eMMC 、PCBs、MCMs、MEMS、IGBT、传感器、小型模块组件等电子元器件/模块冷热测试

WAT是在晶圆制造过程中进行的测试,通过对Die与Die之间Scribe Line的Test Key电学性能的测试,来监控Fab制程的稳定性;CP测试是制造完成后,封测之前进行的电学测试,把坏的Die标记出来,减少封装的成本;FT是Die切割,打磨,封装后进行器件功能性的测试,可以评价封测厂的封装水平,只有所有的测试都通过后,才可以应用到产品上。